CMOSアニーリングの変遷

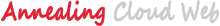

小数など連続変数に対応した「Relaxed MA」

2024年6月

離散変数と連続変数の両方を含む最適化問題を解くアルゴリズムを開発したことにより計算できる桁数を大幅に拡大

これまで二値変数最適化問題の計算技術として発展してきたCMOSアニーリング。この二値変数に加えて小数など連続値も含む計算を可能にするアルゴリズムを開発し最適化計算精度を飛躍的に向上させることを実現しました。

保険ポートフォリオ最適化に適用することで、これまで最小1千万円単位であったものを1円単位で計算でき、一度の計算で多くの組合せを考慮することも可能となりました。

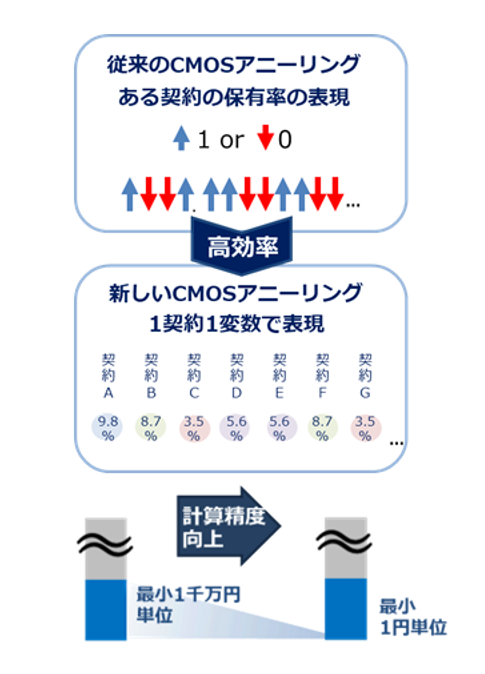

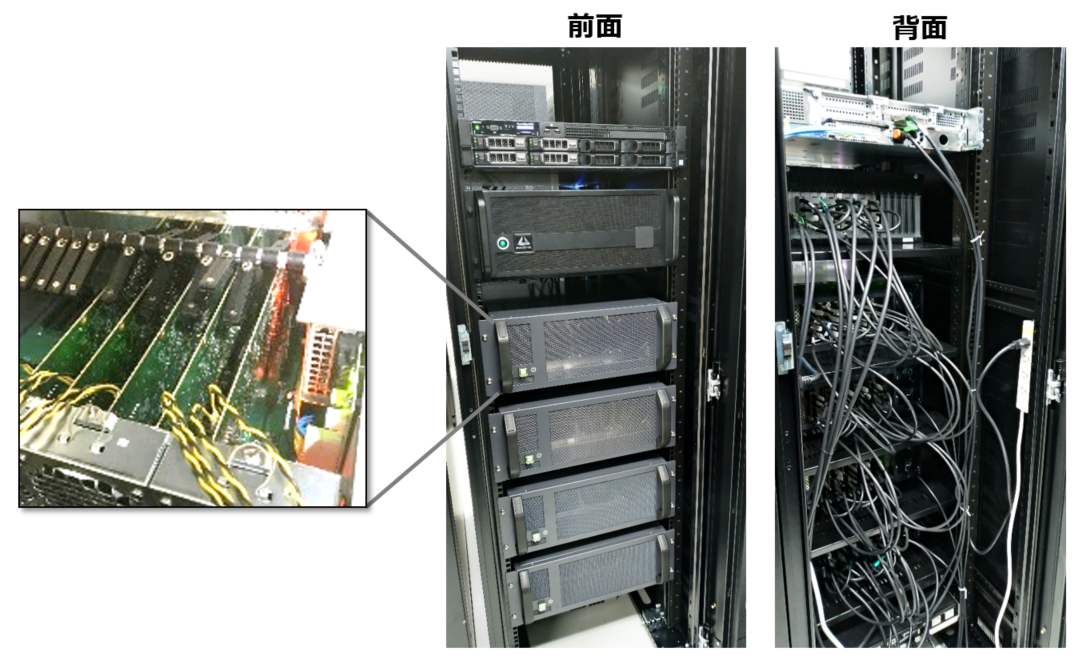

3×3×9ボード=81チップ接続動作を実証(1.3Mスピン)

2021年11月

2021年2月発表の9チップ接続ボードどうしを縦・横に接続することで81チップの協調動作を実証

ボードをつなぎさえすれば無限に大きくできることを実証。さらなる大規模化の要求にこたえられることを証明しました。

3×3=9チップ接続動作を実証(144kスピン)

2021年2月

さらに大きく。3方向に9チップ接続したCMOSアニーリングマシンの誕生

名刺サイズプロトの発表から2年。同NEDOプロジェクトの成果として新たに、縦・横・斜めに9枚のCMOSアニーリングチップを接続して144kスピンに対応するCMOSアニーリングマシンとして発表。2次元上には接続すれば無限に大きくできることを実証。今後のさらなる大規模化の要求にこたえます。

本クラウドサービスに実装しサービス提供しているASIC版アニーリングマシンです。

Annealing Cloud Web 向けGPU(King's graph版)を実装

2020年8月

アプリ探索を加速するため当サイトのAPIで実行できるソフトウェア版アニーリングマシンを提供開始。

ASIC版CMOSアニーリングマシンのアニーリングをGPU上のソフトウェアとして実行する環境を当サイトに実装。256kスピンに対応し32ビットの係数幅を持ちます。ハードウェアでは解けない問題をテストしてアプリケーション探求の加速を狙います。

本クラウドサービスに実装しサービス提供しているGPU(King's graph)版アニーリングマシンです。

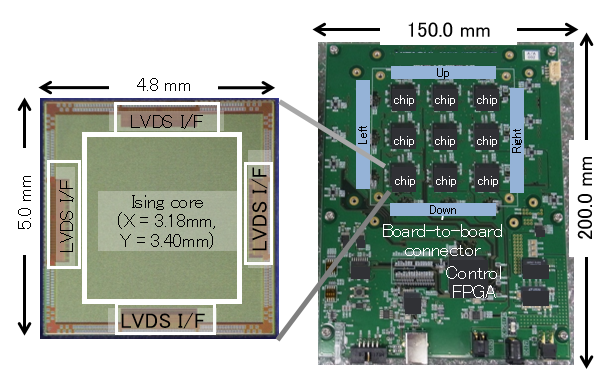

Momentum Annealing版を発表

2019年8月

ついに全結合CMOSアニーリングを発表。それがMomentum Annealing(MA)版

全結合のイジングモデルの基底状態探索が出来るアルゴリズムを発表。GPUに実装し従来の最適化されたSA法と比較して250倍の性能で計算できることを確認。

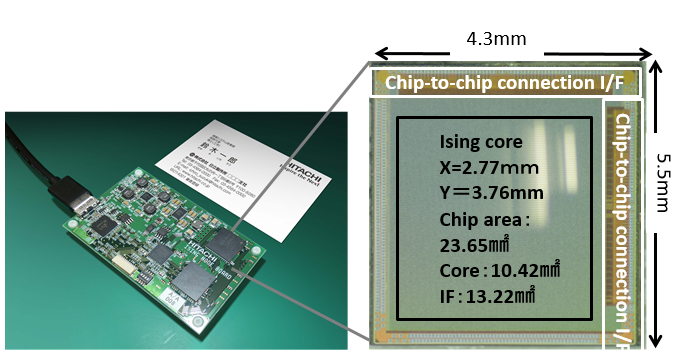

More...名刺サイズCMOSアニーリングマシンを発表(60kスピン)

2019年2月

2チップ接続名刺サイズCMOSアニーリングマシンをNEDOプロジェクト成果として開発

2016年に開始したNEDOプロジェクトにおいて、日立はCMOSアニーリングマシンの大規模化開発に取り組み、2枚のチップを接続して動作させるプロトタイプを試作。わずか名刺大の世界最小ハードウェアでありながら、30,976×2=61,952スピンに対応し、消費エネルギーも少なくUSB接続で作動するアニーリングマシンが生まれました。エッジデバイスに組み込んで動作可能であることを示しました。

Annealing Cloud Web オープン

2018年8月

FPGAを25枚接続し大規模CMOSアニーリングマシンを実証(100kスピン)

2018年6月

FPGAを25枚接続して巨大CMOSアニーリングマシンとして動かすことに成功

2018年、FPGAを25枚接続して1台のCMOSアニーリングマシンとして作動することに成功しました。これにより102,400スピンの大規模組合せ最適化問題に対応するハードウェアを実現。この成果を発展させ、チップの接続による後のASICプロトタイプの拡張が実現しました。デジタルで計算することでスケーラブルな計算が実現できることを示しました。

FPGA版 CMOSアニーリングマシンを試作。解精度向上を実現

2016年11月

実装とアプリの探求のためFPGAプロトタイプを第2世代として試作

2016年に発表した第2世代プロトタイプはFPGAで実装し、パラメータの処理を複数の要素で共有することによってこれまでと同じマシン面積で回路を1/10に抑えることを実現するとともに、計算精度を向上させることにも成功しました。また、programmableなプロトタイプを活用することにより、その後のCMOSアニーリングマシンの研究開発をさらに加速。

NEDO IoT横断プロジェクト開始

2016年8月

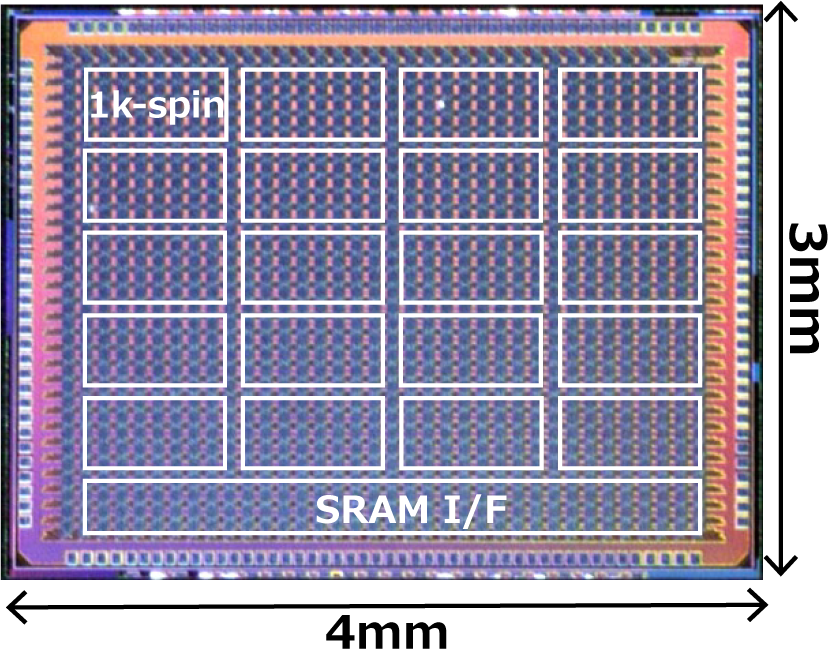

初代CMOSアニーリングチップを発表(20kスピン)

2015年2月

初代CMOSアニーリングチップをISSCC2015において発表

半導体CMOSで実装し、室温で動作する世界初のイジングマシンであるCMOSアニーリングマシンを発表しました。